# PROPOSAL TO SETUP INTEL UNNATI MULTI-DISCIPLINARY LABS

#### **CADMAXX SOLTIONS PVT. LTD**

#2095, 5th Main, 9th Cross, RPC Layout, Vijayanagar, Bengaluru – 560 104 Tel: +91 98444 81112/+91 76205 34337

UmeshRR@cadmaxx.com / Dinesh.Biradar@cadmaxx.com

# Contents

| Executive Summary                                                                                           | 2        |

|-------------------------------------------------------------------------------------------------------------|----------|

| Introduction                                                                                                | 3        |

| Identified Need                                                                                             | 3        |

| What is INTEL Unnati Program                                                                                | 5        |

| INTEL UNNATI – Data Centric Labs                                                                            | 6        |

| HIGH LEVEL LAB DESIGN                                                                                       | 7        |

| Course Details                                                                                              | 8        |

| AI/ML/ADAS:                                                                                                 | 8        |

| Digital Logic And Embedded Systems:                                                                         | 9        |

| FPGA – Basics & AI Acceleration (30 hrs)                                                                    | 10       |

| Embedded Systems                                                                                            | 10       |

| Artificial Intelligence                                                                                     | 10       |

| Acceleration Stack for Xeon CPU with FPGAs                                                                  | 10       |

| Value Adds                                                                                                  | 11       |

| Access to Intel DevCloud for the Edge                                                                       | 11       |

|                                                                                                             | 11       |

|                                                                                                             |          |

| FPGA Project development Kits                                                                               | 12       |

| FPGA Project development Kits                                                                               |          |

|                                                                                                             | 13       |

| Conclusion                                                                                                  | 13       |

| ConclusionBill of Materials                                                                                 | 13<br>14 |

| Conclusion  Bill of Materials  Bill of Materials for AI Starter Labs                                        |          |

| Conclusion  Bill of Materials  Bill of Materials for AI Starter Labs  Bill of Materials for AI Research Lab |          |

# **Executive Summary**

India aims to become a \$1 trillion digital economy by 2025, and this requires significant investment in 21st century infrastructure and software capabilities.

The value pool is fundamentally shifting away from legacy technologies and towards digital—automation, cloud, cybersecurity, mobile, artificial intelligence (AI), 3-D printing, internet of things (IoT), big data analytics, and social media—at a pace even faster than anticipated just a few years ago. To emerge as an Information Technology and Business-Process Management (IT-BPM) leader, India needs to preparepeople to develop advanced capabilities in these technologies.

Enhancing the curriculum in higher education so that students and faculty are equipped with these data-centric skills is an important foundational element to make progress on this digital transformation journey.

To propel India's digital economy transformation, it is imperative that the higher education system in the country bridges this gap by developing new curricula and offering courses in emerging technologies. The National Education Policy 20201 recognises this and stresses the need for greater industry-academic linkages, and for higher education institutions to focus on research and innovation.

This proposal dwells in depth on how Intel® Unnati Program can keep pace with fast changing industry needs and expectations and provide the academic institutions capability in the futuristic technology at an affordable investment and in a definitive time. The Intel® Unnati Program spurs the intelligent and exploratory mind of the academician and provides a canvas for the searching mind to create innovative assets.

#### Introduction

Artificial Intelligence has unleashed a new era of creativity and ingenuity. Today, Intel® technologies power some of the most promising AI use cases in business, society, and research. From massive cloud to tiny device, Intel turns the promise of a transformative AI model into a global-scale reality.

Intel's portfolio of Xeon® scalable processors, combined with Al-optimised FPGAs, VPUs, memory and storage technologies, and software solutions ease the processfor deploying Al and data analytics in real-world applications.

Intel is committed to unlocking the promise of AI. To drive AI innovation, Intel ismaking strategic investments spanning R&D, technology, and partnerships with business, government, academia and community groups.

#### **Identified Need**

Industry and Education providers must collaborate to offer a significant curriculum, right training of skills, enhance the job opportunities and gain the hands-on experiential learning quotient in education. By gaining information on the job roles, job needs, matching of skills imparted to job functions increases the transparency.

The objectivity in performance measurement must be created.

The integrated management of education for the employment activities of various stakeholders involves youth in aligning the choices with employment opportunities, create trust between the employer, educator, and youth.

Hence, the need of the hour is to ensure that there is continuous interaction and integration of efforts between the industry and academic institutions. The steps for growth of the integrated model of skill education is depicted here under:

Hence, it is imperative that the academic institutions in addition to the current curricula that they are providing in their traditional approach, needs to adopt additional skill development capabilities which takes all the students and the faculty together across these three steps of future readiness.

To support and extend the solution, **Intel Unnati Program** is the need of the hour for various skill development programs. The primary aim of any premier education institution is to create capability amongst students to become successful by adopting latest technologies and acquires skills that enable them to help the enterprises reach goals efficiently. However, striving for this type of excellence is often easier said than done. **Intel Unnati Program** is a key component of success in this direction.

# What is INTEL Unnati Program

With the Intel® Unnati Program, you can keep pace with fast changing industry needs and expectations.

It will help Institutes

#### Equipyour students with industry relevant data centric skills

In this age of data explosion, there is immense opportunity. Give your students the edge by equipping them with data-centric skills that will help them glean better insights and develop high-value solutions.

#### Unleash your students' creative potential

We, in India, have an incredible opportunity to unleash the creative potential of the largest student population in the world by training them in the right skills to drive India's digital transformation.

#### Build a strong reputation

With an Intel co-branded lab, you can be recognized as an institute that is committed to train your students in the latest technology to prepare them for industry and focus on faculty development.

#### Build capability for the long term

Establish your leadership and maintain it with the help of our System Integrator associates, who will get you Intel's recommendations for end-to-end Technology Labs set up, course content, and the training to go with it.

#### Leverage our System Integrator Associate Network

Be it training, customizations of your labset up, or your maintenance and supportrequests, you can rely on our strong System Integrator Associate Network forall your needs

#### Showcase New Skills

Students are awarded an Intel co-branded certificate at the completion of their course.

#### Coursework that Enables Learning by Doing

With an emphasis on hands-on exercises, the course covers Machine Learning, Deep Learning, and deploying Models using Intel Distribution of OpenVino™ toolkit on modern Intel® architecture.

#### Custom Lab Deployments

Our System Integrator associates will assist you for customizations to your lab setup and training contentto suit your needs.

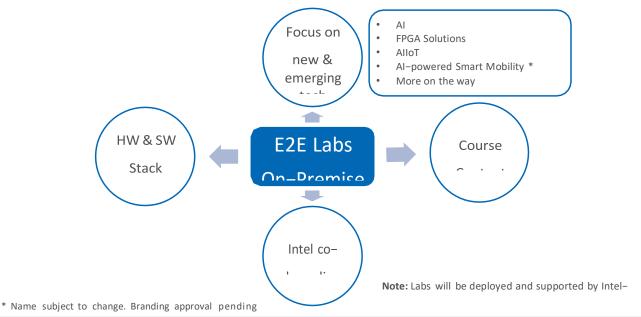

### **INTEL UNNATI - Data Centric Labs**

# Intel® Unnati - Data-Centric Labs in Emerging Technologies

Intel Confidential – For discussion purposes only

intel

6

# **HIGH LEVEL LAB DESIGN**

#### **On-Premise**

intel

Intel Confidential – For discussion purposes only

# **Course Details**

AI/ML/ADAS:

| Machine Learning on Mode                                                                                          | ern Intel Arch (Duration: Approx15hrs)                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prerequisites: Python programming Calculus Linear algebra Statistics                                              | Learning Outcomes: Supervised learning algorithms Key concepts like under – and over–fitting, regularization, and cross – validation How to identify the type of problem to be solved, choose the right algorithm, tune parameters, and validate a model Unsupervised learning                                                                                                   | <ul> <li>Lab Exercises:</li> <li>Supervised Learning and K Nearest Neighbors</li> <li>Train Test Splits, Cross Validation, and Linear<br/>Regression</li> <li>Regularization and Gradient Descent</li> <li>Logistic Regression and Classification Error Metrics</li> <li>Clustering Methods</li> </ul>                                                                                                                                                                                                                                                                           |

| Deep Learning on Modern                                                                                           | Intel Architecture (Duration: Approx18 hrs)                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Prerequisites: Python programming Calculus Linear algebra Statistics Machine Learning Course                      | <ul> <li>Learning Outcomes:</li> <li>Techniques, terminology, and mathematics of DL</li> <li>Fundamental neural network architectures, feedforward networks, convolutional networks, and recurrent networks</li> <li>How to appropriately build and train models</li> <li>Various deep learning applications</li> <li>How to use pre -trained models for best results</li> </ul> | Lab Exercises:  Handwritten Image Detection with Keras using MNIST data  Building a CNN to classify images in the CIFAR — 10 Dataset  Transfer Learning using MNIST data  Using Pre –Trained Models  Classifying CIFAR–10 with Data Augmentation  Hands on E2E workflow using an image classification problem.                                                                                                                                                                                                                                                                   |

| ADAS Alert Analysis using Inte                                                                                    | el Distribution of OpenVino Toolkit (Duration: Appro                                                                                                                                                                                                                                                                                                                             | x10 hrs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Prerequisites: Python programming Calculus Linear algebra Statistics Machine Learning Course Deep Learning Course | Learning Outcomes: Learn about Intel® Distribution of OpenVino toolkit for DL inference Real-time data analysis                                                                                                                                                                                                                                                                  | <ul> <li>Collect real -time data from N vehicles over a period of 30 days, with ADAS sensors (Dashcams optional)</li> <li>Lab Exercises:         <ul> <li>Normalization of real -world data from sensors on across time</li> <li>User-specific data analysis (alert types, behaviour categorization)</li> <li>Population rank based on metrics</li> <li>Identification of hotspots on road network, ahead of possible accidents (project)</li> <li>Use Al/ML to identify near- accident events from large video footage (project - optional with Dashcam)</li> </ul> </li> </ul> |

\_\_\_\_\_

#### Digital Logic and Embedded Systems:

| Minimum Suggested Specifications for 30 Users |                    |                                                          |  |

|-----------------------------------------------|--------------------|----------------------------------------------------------|--|

| Server/Workstations                           | Boards             | Software                                                 |  |

| 15 (minimum 10) x Intel® Core™ i3 processor   | 10 x DE10-Lite*    | Intel® Quartus® Lite with FPGA libraries supported along |  |

| based PCs with at least 4 GB RAM              | 2 x DE10-Nano*     | with ModelSim* FPGA Starter editionand Intel® SoC        |  |

|                                               | 2 x DE1-SoC*       | Embedded Development Suite (SoC EDS) standard edition    |  |

|                                               | 1 x DE10-Standard* | and Intel® HLS Compiler                                  |  |

|                                               |                    |                                                          |  |

|                                               |                    |                                                          |  |

|                                               |                    |                                                          |  |

#### Project Development Kits

for semester long capstones and senior designs

Self Balancing Robot: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=238&No=1096

Servo Motor Kit: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=238&No=1028

A-Cute Car Robotic Kit: https://www.terasic.com.tw/cgibin/page/archive.pl?Language=English&CategoryNo=238&No=1018&PartNo=1

Terasic Spider: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=238&No=994&PartNo=6

Multi Touch LCD Module: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=653

# FPGA – Basics & Al Acceleration (30 hrs)

| Digital Logic                                                                                       |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |  |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Prerequisites:     • Fundamentals of Electronics     • Boolean Logic     • Any Programming Language | <ul> <li>Learning Outcomes:</li> <li>Combinational and Sequential logic</li> <li>Key logic elements - storage clocks and memory</li> <li>How to implement finite state machines in circuitry</li> <li>How to write, compile, synthesize and download hardware designs for FPGAs</li> </ul>                                     | Lab Exercises:  • Switches, Lights and Multiplexers, Numbers and displays  • Latches, FFs & Registers, Counters, Timers and Real-time clocks  • Adders, Subtractors and Multipliers, Finite State Machines  • Memory blocks, A Simple Processor, An Enhanced Processor • Implementing Algorithms in hardware and Basic DSP  |  |

| Embedded Systems                                                                                    |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |  |

| Prerequisites: • Familiarity with the Bresenham line-drawing algorithm • Linux Kernel modules       | Learning Outcomes:  • Writing Linux Kernel modules that use device drivers  • Designing user level programs that use available hardware resources  • Graphics and animation on a VGA display  • Use the ADXL345 accelerometer                                                                                                  | Lab Exercises:  • Get started with Linux  • Develop Linux Programs that communicate with FPGAs  • Character device drivers and Using Character device drivers  • Use ASCII graphics for animation & Intro to graphics & animation  • Use the ADXL 345 accelerometer  • Introduction to audio and multithreaded applications |  |

| Artificial Intelligence                                                                             |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |  |

| Prerequisites:  • Digital Logic course  • Embedded Systems course                                   | Learning Outcomes:  Using the Intel SDK for OpenCL applications Improvements OpenCL kernels can offer in various situations How FPGAs can be used to accelerate Al inference                                                                                                                                                   | Lab Exercises:  Get started with the Intel SDK for OpenCL applications  Accelerating Computer Vision Techniques  Lane detection for Autonomous driving  Classification of Handwritten digits – Linear Classifier  Classification of Handwritten digits – CNN Classifier                                                     |  |

| Acceleration Stack for Xeon CPU with FPGAs                                                          |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |  |

| Prerequisites: • Basic Understanding of FPGAs                                                       | Learning Outcomes:  • Know the basics of using RTL tools and methods to develop an accelerator function for the FPGA that interacts with the acceleration stack  • How to develop an AFU for the FPGA  • Understand the CCI-P that connects the accelerator function  • Use the OPAE to interact with the accelerator function | Lab Exercises:  Creating a host application  Simulating with ASE  Add a scratch register to AFU and host application  Generate the AFU bitstream to configure the FPGA                                                                                                                                                      |  |

\_\_\_\_\_

#### Value Adds

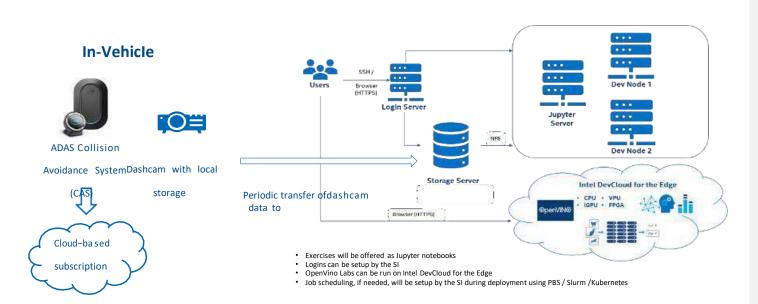

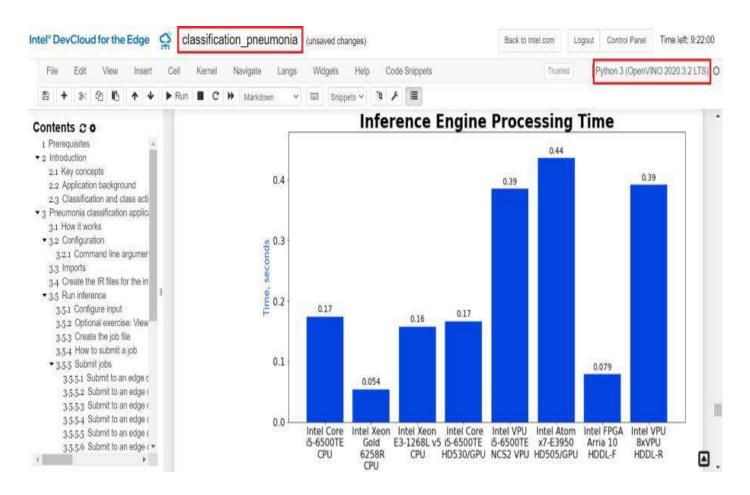

#### Access to Intel DevCloud for the Edge

#### FPGA Project development Kits

(for semester long capstones and senior designs)

- Self- Balancing RobotServo Motor Kit

- A-Cute car robotic kitTerasic Spider

- Multi Touch LCD Module

# IoT Reference Implementations

https://software.intel.com/content/www/us/en/develop/topics/iot/reference-mplementations.html

# Social Distance Detection:

# Human & Vehicle Detection:

#### Conclusion

**Intel Unnati Program** for Futuristic Technologies ensures that the academic institutions equip themselves with the ever-changing technology tools and capabilities on one hand and skill the students with such futuristic technologies. The program creates capability within the academic institution to address the dual requirement of being a part of innovative growth and the skilling of students calls for a setting up of Center of Excellence by providing the platform for doing both.

This proposal details how **Intel Unnati Program** provide the academic institutions capability in the futuristic technology at an affordable investment and in a definitive duration. By engaging in the program the academic institutions, their faculty, research scholars, and the students stand to gain by way of increased traction from the industry for research, opportunity for the faculty and research scholars to present papers and create innovative re-usable solutions, and students to increase their employability by acquiring globally recognized skills.

We look forward to being partner in your esteemed institution's journey in achieving academic excellence and create a platform for regular industry academician interaction.

We are authorized to present this proposal to you as Intel authorized partner and accordingly submit this proposal for your kind consideration and approval.

| Signature of Authorized Signatory: |       |

|------------------------------------|-------|

| Name:                              |       |

| Designation:                       |       |

| Company Name and Seal:             | Date: |

# **Bill of Materials**

# Bill of Materials for AI Starter Labs

| 1x Node<br>(Minimum 1<br>PhysicalCore<br>and 8GB RAM per<br>user)                                                                                            | <ul> <li>Dual Intel® Xeon® Gold 5318Y, 24 cores,<br/>2.1 GHz base frequency, 36 MB cache</li> <li>256 GB Memory: 16 x 16 GB of 2993 MHzDDR4<br/>ECC Registered Memory</li> <li>1 TB SSD</li> </ul>                                | <ul> <li>Ubuntu* 18.04</li> <li>Intel® oneAPI Base Toolkit</li> <li>Intel® Al Analytics Toolkit</li> <li>Horovod*+Intel® MPI (optional, for distributed DL training with TensorFlow*)</li> <li>JupyterHub* and JupyterLab*</li> <li>Keras*, ipykernel*, Seaborn*</li> <li>+ other packages as required by exercises</li> <li>Note: Check https://software.intel.com/ containers</li> <li>For available Al containers</li> </ul> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1xLogin+StorageServer                                                                                                                                        | <ul> <li>Intel® Xeon® Silver 4310, 12 cores, 2.1 GHz base frequency, 18 MB cache, 128 GB RAM</li> <li>At least 10 GB disk space per user (Capacity should based on estimate of total users who would utilise this lab)</li> </ul> | • Ubuntu* 18.04                                                                                                                                                                                                                                                                                                                                                                                                                 |

| + Network Router with 4 RJ45 1Gbps Port, Power Delivery Unit (PDU), Patch Cables and Power Cable  OpenVino™ labs will be run on Intel® DevCloud for the Edge |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

\_\_\_\_\_

# Bill of Materials for Al Builder Lab

| Al Builder Lab Infrastructure         | Minimum Sugg                                               | gested Specifications for 30 Users                                             |                                                              |

|---------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------|

|                                       | 3 x Nodes                                                  | • Dual Intel® Xeon® Gold 5318Y, 24 cores,                                      | • Ubuntu* 18.04                                              |

|                                       | (Minimum 2                                                 | 2.1 GHz base frequency, 36 MB cache                                            | <ul> <li>Intel<sup>®</sup> oneAPI Base Toolkit</li> </ul>    |

|                                       | PhysicalCores                                              | • 256 GB Memory: 16 x 16 GB of 2993                                            | <ul> <li>Intel<sup>®</sup> AI Analytics Toolkit</li> </ul>   |

|                                       | and 8GB RAMper                                             | MHzDDR4 ECC Registered Memory                                                  | • Horovod* + Intel® MPI (for                                 |

|                                       | user)                                                      | • 1 TB SSD                                                                     | distributed DLtraining with                                  |

|                                       | Note:                                                      |                                                                                | TensorFlow*)                                                 |

|                                       | You could use 1                                            |                                                                                | <ul> <li>Intel® Extension for PyTorch*<br/>(IPEX)</li> </ul> |

|                                       |                                                            |                                                                                | • Intel® Distribution of                                     |

| For institutions that are seeking to  | node as the                                                |                                                                                | OpenVINO™ Toolkit                                            |

| go beyond lab exercises and investing | Jupyter* server                                            |                                                                                | Note: Check                                                  |

| in the next generation of AI Builders |                                                            |                                                                                | https://software.intel.com                                   |

|                                       |                                                            |                                                                                | /containers for available AI conta                           |

|                                       |                                                            |                                                                                | Jupyter* Server:                                             |

|                                       |                                                            |                                                                                | • Ubuntu* 18.04                                              |

|                                       |                                                            |                                                                                | <ul> <li>JupyterHub* and JupyterLab*</li> </ul>              |

|                                       |                                                            |                                                                                | <ul> <li>Keras*, ipykernel*, Seaborn*</li> </ul>             |

|                                       |                                                            |                                                                                | + other libs as required by                                  |

|                                       |                                                            |                                                                                | exercises                                                    |

|                                       | 1 x Storage Server                                         | Rackmount 4 - Bay Network* Attached Sto                                        |                                                              |

|                                       |                                                            | with at least 50GB disk space per user                                         |                                                              |

|                                       |                                                            | (Capacityshould be based on estimate of total users whowould utilise this lab) |                                                              |

|                                       | 1 v l agin Comvon                                          | • Intel® Xeon® Silver 4310, 12 cores, 2.1 GHz                                  | • Ubuntu* 18.04                                              |

|                                       | 1 x Login Server                                           | base frequency, 18 MB cache, 128 GB RAM, 5                                     |                                                              |

|                                       |                                                            | SSD SSD                                                                        |                                                              |

|                                       | + Network Router wit                                       | h 1Gbps Ports, Network Switch, Rack Cabinet, Powe                              | r Delivery Unit (PDU), Patch                                 |

|                                       | Cablesand Power Cable                                      |                                                                                |                                                              |

|                                       | +Software for job scheduling and queueing                  |                                                                                |                                                              |

|                                       | OpenVino™ labs will be run on Intel® DevCloud for the Edge |                                                                                |                                                              |

#### Bill of Materials for AI Research Lab

| 4-8x Nodes                                                                                      | Dual Intel® Xeon® Gold 6330, 28 cores, 2.0 base frequency, 42 MB cache • 256 GB Memory: 16 x 16 GB of 2933 MHzE ECC Registered Memory • 1 TB SSD                                                                                                                                                   | • Intel® oneAPI Base Toolkit                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1xFPGAInferenceNode (only Qualified <sup>†</sup> Servers)                                       | <ul> <li>Intel® Xeon® Silver 4314, 16 cores, 2.4 GHz base frequency, 24 MB cache</li> <li>128 GB Memory: 8 x 16 GB of 2667 MHz DDR4ECC Registered Memory</li> <li>1 TB SSD</li> <li>1-2 Intel® Programmable Acceleration Cardwith Intel Arria® 10 GX FPGA<sup>†</sup></li> </ul>                   | <ul> <li>Ubuntu* 18.04</li> <li>Intel® oneAPI Base Toolkit</li> <li>Intel® AI Analytics Toolkit</li> <li>Intel® FPGA Add-On for oneAPI Base Toolkit</li> <li>Intel® Distribution of OpenVINO™ Toolkit(LTS Release</li> </ul> |

| 1xVPUInferenceNode                                                                              | <ul> <li>Intel® Xeon® Silver 4314, 16 cores, 2.4 GHz base frequency, 24 MB cache</li> <li>128 GB Memory: 8 x 16 GB of 2667 MHz ECC Registered Memory</li> <li>1 TB SSD</li> <li>1-2 Intel® Vision Accelerator Design With Movidius™ Vision Processing Unit with supportfor up to 8 VPUs</li> </ul> | <ul> <li>Ubuntu* 18.04</li> <li>Intel® oneAPI Base Toolkit</li> <li>Intel® AI Analytics Toolkit</li> <li>Intel® Distribution of OpenVINO™ Toolkit</li> </ul>                                                                 |

| 1 x Login Server                                                                                | <ul> <li>Intel<sup>®</sup> Xeon<sup>®</sup> Silver 4310, 12 cores, 2.1 GHz<br/>base frequency, 18 MB cache, 128 GB RAM,<br/>SSD</li> </ul>                                                                                                                                                         | • Ubuntu* 18.04                                                                                                                                                                                                              |

| 1 x Storage Server                                                                              | • TrueNAS* 1U 120 TB or equivalent                                                                                                                                                                                                                                                                 | TrueNAS* Open Storage OS                                                                                                                                                                                                     |

| Ethernet Cards                                                                                  | <ul> <li>Intel® Ethernet 700 Series Network Adapters</li> <li>Upgrade to Intel® Ethernet 800 Series, which offers upto 100GbE, when available</li> </ul>                                                                                                                                           |                                                                                                                                                                                                                              |

| + Network Router with 25-100Gbps Ports, Power Delivery Unit (PDU), Patch Cables and Power Cable |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                              |

| +Software for job scheduling and                                                                | queueing                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                              |

#### Important notes relating to all AI Lab Configurations

- 1. If Network File System (NFS) is installed, then all Intel software tools need to be installed only once through anyof the compute nodes on to a network location visible to all nodes. If you don't have NFS, then only the runtime components of Intel tools need to be installed on the hard drive of every node.

- 2. Initialise MPI environment first before installing Horovod\*. (source setvars.sh)

## Bill of Materials for Digital Logic and Embedded System

| Minimum Suggested Specifications for 30 User                                                   | S                                                                             |                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Server/Workstations  • 15 (minimum 10) x Intel® Core™ i3 processorbased with at least 4 GB RAM | Boards • 10 x DE10-Lite* • 2 x DE10-Nano* • 2 x DE1-SoC* • 1 x DE10-Standard* | Software  • Intel® Quartus® Lite with FPGA libraries supported a with ModelSim* FPGA Starter editionand Intel® S Embedded Development Suite (SoC EDS) standard edition and Intel® HLS Compiler |

#### **Project Development Kits**

for semester long capstones and senior designs

- Self Balancing Robot: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=238&No=1096

- Servo Motor Kit: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=238&No=1028

- A-Cute Car Robotic Kit: https://www.terasic.com.tw/cgibin/page/archive.pl?Language=English&CategoryNo=238&No=1018&PartNo=1

- Terasic Spider: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=238&No=994&PartNo=6

- Multi Touch LCD Module: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=653

#### **FPGA Courses**

- 1) Digital Logic

- 2) Computer Organisation

- 3) Embedded Systems

## Bill of Materials for FPGA and Artificial Intelligence Lab

| Minimum Suggested Specifications for 30 Users                                                                                                                                                                                                                                                      |                                                                                      |                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Server/Workstations  • Tools/License Server: Intel® Core™ i7/i9 orIntel®  Xeon processor, 64 GB RAM, 500 GBSATA HDD  running Linux OS, 24" Monitor, Keyboard and                                                                                                                                   | Acceleration Cards  • 2 x Intel® Arria® 10  FPGAPAC  or  • 1 x Intel® Arria® 10 FPGA | Software  • Intel® Quartus® Standard DesignSoftware and Intel® for OpenCL™ is included  • Intel® Distribution of OpenVINO™Toolkit  • Intel® oneAPI Base Toolkit |

| <ul> <li>Mouse Optional: Graphics Card</li> <li>1 x Qualified Server for housing the Intel®</li> <li>Programmable Acceleration Card (PAC): Refer to Qualified Servers list below</li> <li>15 (minimum 10) x Intel® Core™ i3 processor based PCs with at least 4 GB RAM for server-based</li> </ul> | PAC and 1 x Intel® Stratix®<br>10 FPGA PAC (D5005)                                   | <ul> <li>Intel® FPGA Add-on for oneAPIBase Toolkit</li> <li>Intel® Acceleration Stack (supports OpenCL™, DPC++, RTL based descriptions)</li> </ul>              |

| license access                                                                                                                                                                                                                                                                                     |                                                                                      |                                                                                                                                                                 |

#### **Project Development Kits**

for semester long capstones and senior designs

- Intel® Arria® HAN Pilot: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=228&No=1133

- Intel® Arria® Flik: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=228&No=1237

Users can also try out the one API or FPGA DevCloud for a limited period of time:

- Intel® DevCloud for the Edge: https://devcloud.intel.com/edge/home

- Intel® DevCloud for oneAPI: https://devcloud.intel.com/oneapi

- $\bullet \ \mathsf{FPGA} \quad \mathsf{DevCloud:} \quad \mathsf{https://software.intel.com/content/www/us/en/develop/tools/devcloud/fpga.html}$

Qualified Servers for Intel® FPGA PAC:

- With Intel® Arria® 10 GX: https://www.intel.com/content/www/us/en/programmable/products/boards and kits/dev-kits/altera/acceleration-car arria-10-gx/buy.html

- D5005: https://www.intel.com/content/www/us/en/programmable/products/boards\_and\_kits/dev-kits/altera/intel-fpga-pac-d5005/buy.html

# Communications and High-Speed DataAcquisitionLab

| Minimum Suggested Specifications for 30 Users       |                             |                                              |

|-----------------------------------------------------|-----------------------------|----------------------------------------------|

| Server/Workstations                                 | Boards and Cards            | Software                                     |

| • Tools/License Server: Intel® Core™ i7/i9 orIntel® | • 1 x Intel® Arria® 10 GX   | • Intel® Quartus® Standard DesignSoftware is |

| Xeon processor, 64 GB RAM, 500 GBSATA HDD runn      | withADI* AD9371*            | included along with the development board    |

| Linux OS, 24" Monitor, Keyboard and Mouse           | • 1 x Intel® Stratix® 10 GX |                                              |

| Optional: Graphics Card                             | with ADI* AD9174*           |                                              |

|                                                     | Select board based on       |                                              |

|                                                     | required peripherals and    |                                              |

|                                                     | connectors.                 |                                              |

#### **Project Development Kits**

for semester long capstones and senior designs

- $\bullet \ \mathsf{RFS:} \ \textit{https://}\underline{\textit{www.terasic.com.tw/cgi-bin/page/archive.pl?} \textit{Language=English\&} \textit{CategoryNo=225\&} \textit{No=1025} \\$

- ADC-FMC: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=73&No=1193& PartNo=2#section

#### **Design Examples**

- JESD204B Intel® Arria® 10 FPGA IP Design

- JESD204B Intel® Stratix® 10 FPGA IP Design